# Open Communication

# labZY Firmware Versions 30.19, 30.20

# Contents

| Overview                | 3  |

|-------------------------|----|

| Applicable Devices      | 3  |

| Computer Connections    | 3  |

| UART Interface          | 4  |

| Communication Protocol  | 7  |

| Port Settings           | 7  |

| Commands and Responses  | 7  |

| MICRO Data              | 14 |

| FPGA Data               | 14 |

| Spectrum                | 15 |

| Registers               | 15 |

| Application Information | 16 |

| Revision History        |    |

# Overview

# **Applicable Devices**

This document applies to the following labZY Devices:

nanoMCA nanoMCA-SP nanoXRS nanoDPP

"labZY Device" refers to any of these devices.

# **Computer Connections**

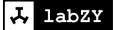

labZY Devices are connected to a computer using one of the following hardware connections: direct USB cable, Ethernet connection through nanoETH module and wireless connection using the nanoBT interface module. When the driver of each one of these connections is installed a virtual COM port is created. Fig. 1 shows the PORT selection dialog of the labZY-MCA software. The selection list include all available virtual COM ports of the labZY Devices.

Fig. 1 PORT selection dialog of labZY-MCA software.

The virtual COM ports emulate standard serial ports and must be configured before being used. The RTS functionality is built-in feature of the nanoBT and nanoRTH modules.

The USB interface cable may provide power to the labZY eliminating the need of an external power supply. The external power supply will be required for the Bluetooth, WiFi and the Ethernet connections. The external power supply can be used as a backup power source when the labZY Devices are connected through the direct USB interface. The USB interface cable and the interface modules are connected to the IO port of the labZY Devices (Fig. 2). The external power is applied through a standard Mini B USB cable to the PWR port of the labZY Devices.

Fig. 2 Interface (IO) and power (PWR) connectors of the labZY Devices.

# **UART Interface**

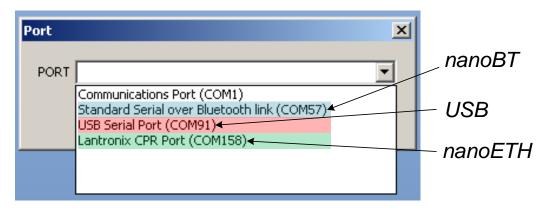

labZY Devices can be interfaced to a microcontroller or a microprocessor based system using an UART port with 3.3V CMOS logic levels. The hardware connection is through a 6 inch (15cm) USB Mini B cable with flying leads shown in Fig. 3.

Fig 3. Cable for connecting the labZY Devices directly to UART ports.

The physical connection between the labZY Device and the UART port of a microcontroller is shown in Fig. 4. The labZY Device can provide +3.3V power and up to 300mA current to the microcontroller or other external circuits. The +3.3V is available on the red lead of the interface cable. If this power is not needed the red lead should be isolated and kept unconnected. Note that the UART interface requires that a +5V external power is supplied to the PWR connector of the labZY Device.

Fig. 4 Microcontroller connection to labZY Devices using UART interface.

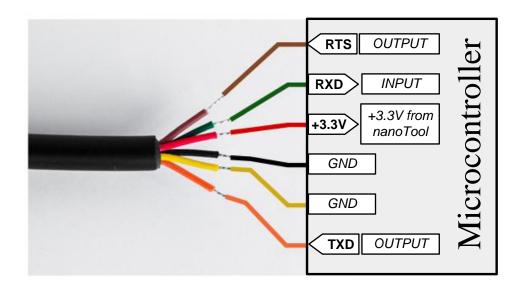

The output line of the microcontroller serial TXD line is connected to the orange lead of the interface cable. The serial input line is connected to the green wire. The microcontroller flow control line RTS is connected to the brown lead. An example of the UART signal waveforms is shown in Fig. 5. Note that the asserted level of the RTS line is logic LOW (3.3V CMOS).

|     |  | - | : |   |   | : |

|-----|--|---|---|---|---|---|

|     |  |   |   |   |   |   |

|     |  |   |   |   |   |   |

| TXD |  | - |   |   |   |   |

| RTS |  | - | : | : | : |   |

|     |  |   |   |   |   |   |

| · · |  |   |   |   |   |   |

Fig. 5 UART interface signals.

The RTS line is used to control the data flow from the labZY Device into the microcontroller and to prevent loss of data. The microcontroller must de-assert RTS line in advance of its receiving buffer becomes full leaving room to receive at least two extra bytes from the labZY Device. This is an important consideration as there might still be data on the line and/or in the labZY Device transmit register which has to be received even after RTS has been de-asserted. When the microcontroller is ready to accept more data it should assert the RTS line and keep it asserted until the receiving buffer gets close to become full. The labZY Device serial port will stop transmission of data as soon as it senses the asserted. The labZY Device can accept all data send by the microcontroller without any interruption of the transmission. Therefore, there is no need of CTS hardware control to the microcontroller. If the microcontroller UART port is equipped with a CTS line then it should be asserted all the time. The timing diagram in Fig. 6 illustrates the data transmission using the RTS control line showing the extra bytes transmitted after the RTS line is de-asserted.

| IMPTOTO       | :                |    | : | Ē | - | :               | :           |              |

|---------------|------------------|----|---|---|---|-----------------|-------------|--------------|

| UART(Rx) X FF | <b>X 70 )( D</b> | 5) |   |   |   |                 | FF X AD     | 1 D5 1 FF )- |

| RTS           |                  |    |   |   |   |                 |             |              |

|               |                  |    |   |   |   | 1 1 <del></del> | <del></del> |              |

|               |                  |    |   |   |   |                 |             |              |

Fig. 6 Pausing data flow using the RTS line.

# **Communication Protocol**

# **Port Settings**

The settings for computer virtual com ports or the UART are as follows:

Baud Rate: 460800 (Firmware Ver 30.19) Baud Rate: 921600 (Firmware Ver 30.20) Data Bits: 8 Stop Bits: 1 Parity: N Handshaking: Hardware, RTS only, UART: RTS asserted state is active LOW

## **Commands and Responses**

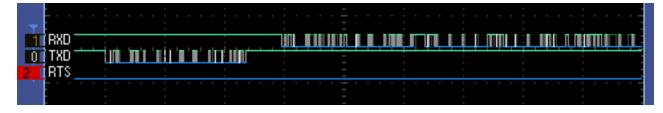

The communication between a labZY Device and the host (computer or microcontroller) is accomplished using commands and responses sent in half-duplex serial transmission as shown in Fig. 7.

Fig. 7 Half duplex serial communication. Shown are the host signals.

The host first sends a command through its TXD line and then listens for a response on its RXD line. In normal operation there should be no simultaneous transmissions on the

TXD and the RXD lines. The labZY Device is a slave device while the host is a master device. Therefore, the master initiates the communication by sending a command. Subsequent commands are sent by the host only after a complete and valid response has been received from the labZY Device or a time-out interval has been reached. The time-out interval should be equal or greater than five seconds.

There are only two commands to access data and to control the labZY Device. The FPGA spectral data (spectrum) and the FPGA registers are accessed as memory data at specific addresses. Each memory location is organized and accessed as a 16-bit word. Each 16-bit word consists of two bytes and two words comprise a long word. Bytes representing words and long words, and words representing long words are stored in the memory in a Little-Endian order.

The host sends and receives the data as a sequence of bytes. The first byte in the sequence is designated as zero byte (BYTE[0]) followed by bytes whose order is incrementally numbered. Bytes are sent in order that follows the Little-Endian rule when the bytes represent words or long words.

The last byte in each command and in the corresponding response from the labZY Device is a check sum byte - **CHKS**. The content of the check sum byte is obtained in two steps. First, a byte sum is calculated by adding all bytes in the command/response excluding the check sum byte. In the byte sum calculation the bytes are treated as unsigned numbers and the overflow is ignored. This sum is stored in the check sum byte. That is, the check sum byte acts as an accumulator of all bytes of the command/response. Secondly, all bits of the obtained byte sum are inverted and the result is incremented by 2 ignoring the overflow. This value is the check sum **CHKS** included as a last byte in the host command or the labZY Device response.

The data is read or written in words starting at an initial address **IADR** or **IADW** respectively. This address is specified in the commands sent by the host to the labZY Device. An **AutoIncrement** bit is a part of the address information send by the host. If the **AutoIncrement** bit in the address field of the command is set to one, then the data address will be incremented automatically after each word reading/writing. The start address is the initial address specified by the host. When reading data and the **AutoIncrement** bit is zero then the data will be read from the same initial address if the number of words to be read is greater than one. When more than one word is to be written with the AutoIncrement bit set to zero then the data at the specified address will be overwritten until the last data word send by the host is written. The host commands also include the number of bytes to be read or written to the FPGA memory - **TNBR** or **TNBW** respectively.

#### READ COMMAND

| 1. Host Read Command               |                                                                                                                                                                                     |

|------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYTE[0,1]:WORD[0] = <b>100</b>     | - Command code.                                                                                                                                                                     |

| BYTE[2,3]:WORD[1] = <b>11</b>      | - Number of bytes in the read command including the check sum byte.                                                                                                                 |

| BYTE[4,5,6,7]:LONG WORD[1] = BIT[2 | 210], BIT22, BIT[3123]                                                                                                                                                              |

| BIT[210]] <b>= IADR</b>            | - FPGA Address of the first data word to be read.                                                                                                                                   |

| BIT22 = AutoIncrement              | - If AutoIncrement=1, FPGA word<br>address automatically increments as<br>words are read beginning with IADR, if<br>AutoIncrement=0 the word at address<br>IADR is read TNBR times. |

| BIT[3123] = <b>0</b>               |                                                                                                                                                                                     |

| BYTE[8,9]:WORD[4] = <b>TNBR</b>    | - The number of FPGA data bytes to be<br>read (twice the number of FPGA data<br>words to be read). TNBR must be an<br>even number.                                                  |

| BYTE[10] = <b>CHKS</b>             | - Check sum byte.                                                                                                                                                                   |

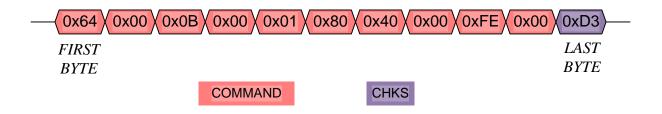

**Example:** Reading 127 FPGA Registers starting from Register[1] at FPGA address 0x8001. Bytes are sent in Little-Endian order.

| WORD[0] | WORD[1] | LONG WORD[1] | WORD[4] | CHKS |

|---------|---------|--------------|---------|------|

| 0x0064  | 0x000B  | 0x00408001   | 0x00FE  | 0xD3 |

Example Check Sum calculation:

ByteSum =  $\sum_{k=0}^{9}$  BYTE[k], ByteSum = 0x2E, ~ByteSum = 0xD1,

CHKS = 0xD1 + 0x02 = 0xD3

#### 2. *labZY Device Response to Host Read Command*

| BYTE[0,1]:WORD[0] = <b>100</b>                                                                                      | - Response Code (same as the Read<br>Command Code).                        |  |  |

|---------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------|--|--|

| BYTE[2,3]:WORD[1] = <b>25 + TNBR</b>                                                                                | - Number of bytes in the response including the check sum byte.            |  |  |

| BYTE[4,5,6,7]:LONG WORD[1] = BIT[2                                                                                  | 10], BIT22, BIT[3123]                                                      |  |  |

| BIT[210] = <b>IADR</b>                                                                                              | - FPGA Address of the first data word to be read (same as in the command). |  |  |

| BIT22 = AutoIncrement                                                                                               | - AutoIncrement bit (same as in the read command).                         |  |  |

| BIT[3123] = <b>0</b>                                                                                                |                                                                            |  |  |

| BYTE[823]: WORD[411] = <b>MICRO Data</b> - Hardware status data from the<br>labZY Device microcontroller, read only |                                                                            |  |  |

| or                                                                                                                  | read volatile.                                                             |  |  |

| BYTE[2423+TNBR]:WORD[1211+TNBR/2] = FPGA DATA                                                                       |                                                                            |  |  |

| BYTE[24+TNBR] = CHKS                                                                                                | - Check sum byte.                                                          |  |  |

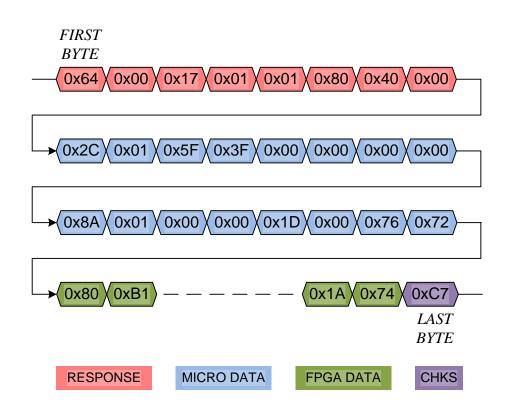

**Example:** labZY Device response to the host command to read 127 FPGA Registers starting from Register[1] at FPGA address 0x8001. Note that the

response always includes the MICRO Data along with the Response and the FPGA Data. Bytes are received in Little-Endian order.

#### WRITE COMMAND

| 1. Host Write Command               |                                                                                                                                                                                                                                                 |

|-------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BYTE[0,1]:WORD[0] = <b>110</b>      | - Command code.                                                                                                                                                                                                                                 |

| BYTE[2,3]:WORD[1] = <b>9 + TNBW</b> | - Number of bytes in the response<br>including the check sum byte. TNBW is<br>the number of FPGA Data bytes to be<br>written. TNBW is always an even<br>number. NOTE: The maximum number<br>of FPGA data bytes in each write<br>command is 512. |

BYTE[4,5,6,7]:LONG WORD[1] = BIT[21..0], BIT22, BIT23, BIT[31..24]

| BIT[210] = <b>IADW</b>       | - FPGA Address of the first data word to be written.                                                                                                                                                                |

|------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT22 = <b>AutoIncrement</b> | <ul> <li>If AutoIncrement=1, FPGA word<br/>address automatically increments as<br/>words are written beginning with IADW,<br/>if AutoIncrement=0 the word at address<br/>IADW is overwritten TNBW times.</li> </ul> |

| BIT23 = <b>1</b>             |                                                                                                                                                                                                                     |

BIT[31..24]= 0

#### BYTE[8..7+TNBW]:WORD[4..3+TNBW/2] = DATA to FPGA

| Check sum byte. |

|-----------------|

|                 |

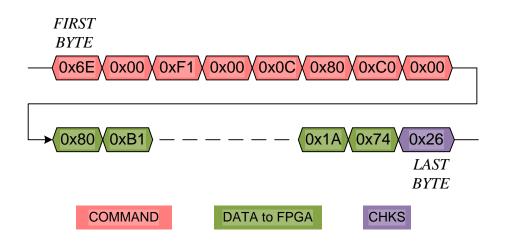

**Example:** Writing data to 116 FPGA Registers starting from Register[12] at FPGA address 0x800C with automatic address increment. Bytes are sent in Little-Endian order.

#### 2. *labZY Device Response to Host Write Command*

| BYTE[0,1]:WORD[0] = <b>110</b>     | - Response Code (same as the Read<br>Command Code).                           |

|------------------------------------|-------------------------------------------------------------------------------|

| BYTE[2,3]:WORD[1] = <b>9</b>       | - Number of bytes in the response including the check sum byte.               |

| BYTE[4,5,6,7]:LONG WORD[1] = BIT[2 | 10], BIT22, BIT[3123]                                                         |

| BIT[210] = <b>IADW</b>             | - FPGA Address of the first data word to be written (same as in the command). |

| BIT22 = AutoIncrement              | - AutoIncrement bit (same as in the write command).                           |

| BIT23 = <b>1</b>                   |                                                                               |

| BIT[3124]= <b>0</b>                |                                                                               |

| BYTE[8] = <b>CHKS</b>              | - Check sum byte.                                                             |

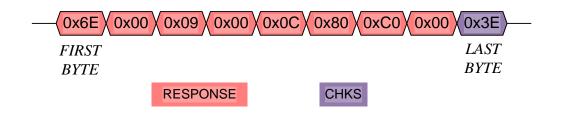

**Example:** labZY Device response to a command to write data to 116 FPGA Registers starting from Register[12] at FPGA address 0x800C with automatic address increment. Bytes are received in Little-Endian order

### MICRO Data

The MICRO Data is a set of eight words that are transmitted as part of the labZY Device response to the host READ COMMAND. WORD[4] (BYTE [8,9]) through WORD[11] (BYTE [22,23]) in the response represent the MICRO Data. The Micro Data is read only data and represent constant or volatile values. The volatile values may change between consecutive readings.

- WORD [4] = Constant, Unsigned, Firmware Version \*100. e.g. 321 = Version 3.21

- WORD [5] = Constant, Unsigned, labZY Device serial number.

- WORD [6] = Volatile, Unsigned, nanoXRS only, Detector Bias Voltage [V];

Other Devices RESERVED.

- WORD [7] = RESERVED.

- WORD [8] = Volatile, Signed, nanoXRS detector temperature;

Other Devices Input D slow ADC reading 0 to 2500 [mV].

WORD [9] = Volatile, Unsigned, nanoXRS cooling power 0 to 330; Divide by 3.3 to find % power.

Other Devices RESERVED.

- WORD [10] = Volatile, Signed, labZY Device internal temperature [C].

- WORD [11] = RESERVED.

### **FPGA Data**

FPGA Data is stored internally in the FPGA. The FPGA Data includes the Spectrum and the Registers. The Spectrum is stored in the FPGA internal memory and can be accessed as words (16bit) at word address 0x000 to 0x7FFF. Address space 0x8000 to 0x807F is used to access 16bit registers that control the hardware and provide status information.

## Spectrum

The labZY Devices store spectral data in a spectrum with a fixed size of 16384 (2<sup>14</sup>) channels. The counts in each channel are stored in a long word using the Little-Endian rule. Therefore, the content of each channel is accessed by reading two words (two memory locations of the memory address space). For instance, the counts of channel zero can be obtained by reading the words at addresses 0x0000 and 0x0001. The counts of the last channel are represented by the words at addresses 0x7FFE and 0x7FFF. With a single read command multiple channels can be read sequentially by setting the address AutoIncrement bit. It is recommended that few thousand channels are read by a single read command, e.g. 4096 channels.

### **Registers**

Physically the registers are part of the FPGA designs supplied by labZY. Registers are used to control the operation of the labZY Device with labZY provided FPGA functionality. The registers are also used to access data such as hardware information, acquisition time, noise measurements etc. From a software point of view these registers are 16-bit words. There are 128 registers located at addresses 0x8000 to 0x807F. The address 0x8000 is the base address. Registers are numbered sequentially from 0 to 127. The register number is the offset relative to the base address.

### **Application Information**

Below are hints in C language. These are just hints and not ready to use routines.

#### /\*variables and defines\*/

| #define READ_DATA_COMMAND 100                            | /*read data command code*/                                                                    |

|----------------------------------------------------------|-----------------------------------------------------------------------------------------------|

| <pre>#define MAX_REGISTERS 128 #define MAXDATA 512</pre> | /*maximum number of bytes that labZY Device will<br>accept with a single write data command*/ |

| <pre>#define S_AUTOINC (1&lt;&lt;22)</pre>               | /*auto-increment bit*/                                                                        |

| <pre>#define SPECTRUM_BASE_ADDRESS</pre>                 | 0x0000 /*base address of the spectrum data*/                                                  |

| <pre>#define REG_BASE_ADDRESS</pre>                      | 0x8000 /*base address of the registers*/                                                      |

| <pre>#define READ_DATA_BYTE_OFFSET 24</pre>              | /*FPGA data byte offset in the response from the                                              |

| <pre>#define READ_MICRO_BYTE_OFFSET 8</pre>              | labZY Device*/<br>/*MICRO data byte offset in the response from<br>the labZY Device*/         |

| <pre>#define READ_DATA_WORD_OFFSET 12</pre>              | /*FPGA data word offset in the response from the labZY Device*/                               |

| <pre>#define READ_MICRO_WORD_OFFSET 4</pre>              | /*MICRO data word offset in the response from the labZY Device*/                              |

| <pre>#define READ_DATA_LONG_OFFSET 6</pre>               | /*FPGA data long offset in the response from the labZY Device*/                               |

| <pre>#define READ_MICRO_LONG_OFFSET 2</pre>              | /*MICRO data long offset in the response from the labZY Device*/                              |

#define MAX\_BYTES\_RECEIVE 16500

/\*maximum number of FPGA bytes to receive from labZY Device in a single transmission\*/

union UNION\_RCV\_BUFFFER{

unsigned char uc[MAX\_BYTES\_RECEIVE];

unsigned short us[MAX\_BYTES\_RECEIVE/2];

unsigned long ul[MAX\_BYTES\_RECEIVE/4];

char sc[MAX\_BYTES\_RECEIVE];

short ss[MAX\_BYTES\_RECEIVE/2];

long sl[MAX\_BYTES\_RECEIVE/4];

} rbuf; /\*host receive data buffer\*/

#define MAX\_BYTES\_SEND 532

union UNION\_SND\_BUFFFER{

unsigned char uc[MAX\_BYTES\_SEND];

unsigned long ul[MAX\_BYTES\_SEND/2];

char sc[MAX\_BYTES\_SEND];

short ss[MAX\_BYTES\_SEND/2];

long sl[MAX\_BYTES\_SEND/4];

} sbuf; /\*host send data buffer\*/

```

#define MAX_BYTES_REGISTER 2*MAX_REGISTERS

union UNION REGISTERS{

unsigned char uc[MAX_BYTES_REGISTER];

unsigned short

us[MAX BYTES REGISTER/2];

unsigned long ul[MAX BYTES REGISTER/4];

char sc[MAX BYTES REGISTER];

short ss[MAX BYTES REGISTER/2];

long sl[MAX BYTES REGISTER/4];

} reg mca; /*register storage*/

/******* READ COMMAND *******/

unsigned short readnanoMCA(unsigned long ul Address, unsigned short us DataBytesToRead,

BOOL b Autoinc){

sbuf.us[0]=READ DATA COMMAND;

/*read data command code*/

sbuf.us[1]=11;

/*total number of bytes in the command*/

if (b autoinc) sbuf.ul[1]=ul Address | AUTOINC; /*read this address

and auto-increment it*/

sbuf.ul[1]=ul Address & ~AUTOINC; /*read this address

else

multiple times*/

sbuf.us[4]=

us DataBytesToRead;

/*number of bytes to be read*/

/******** check sum calculation ********/

sbuf.uc[10]=sbuf.uc[0];

for (i=1; i< 10 ; i++){</pre>

sbuf.uc[10] += sbuf.uc[i];

}

sbuf.uc[10] = ~sbuf.uc[10]+2;

/******** send data via serial port ********/

/* use routine that is supported by OS, compiler, library etc.*/

/* For example: SerialPort.Write( &sbuf.c[0], sbuf.s[1],2000 );

arguments(pointer to the first byte to be sent to serial port, number of bytes to

be sent, time-out in mseconds)*/

return Something; /*Return something that is useful*/

}

unsigned short us_BytesToRead;

unsigned long ul Address;

unsigned long ul_StartRegister;

unsigned short us_NumberRegisterstoRead;

us NumberRegisterstoRead=127;

ul StartRegister =1;

ul Address=REG BASE ADDRESS+ul StartRegister;

us BytesToRead =readnanoMCA(ul Address, us NumberRegisterstoRead*2, S AUTOINC);

/*read all nanoMCA registers, excluding register 0, that is read 127 16-bit registers =

254 bytes*/

```

```

us_BytesToRead =readnanoMCA(SPECTRUM_BASE_ADDRESS, 8192, S_AUTOINC); /*read the

content of spectrum spectrum channels from channel 0 to channel 1023 inclusive (each

channel data has four bytes - unsigned long)*/

us BytesToRead =readnanoMCA(SPECTRUM BASE ADDRESS+10000, 8000, S AUTOINC); /*read

the content of spectrum channels from channel 2500 to channel 4049 inclusive*/

Start a separate tread to read serial port data or use messages to read the serial port

data.

Place sequentially all bytes in the receive buffer buffer rbuf, with the first received

byte placed in rbuf.uc[0]

Read serial port data until the number of the received bytes matches us BytesToRead

once the data is received:

1) Find the check sum

example:*/

unsigned char ucChkSum=0;

for (int i=0; i< READ_FPGA_BYTE_OFFSET+(int)us_DataBytesToRead ; i++){</pre>

ucChkSum += rbuf.uc[i];

}

ucChkSum=~ucChkSum+2;

if(ucChkSum != rbuf.uc[READ FPGA BYTE OFFSET +

(int)us DataBytesToRead]){handleError();}

else (extractData());

/*2)Extract data

Example - populate the register union with the data read from the nanoMCA using

us NumberRegisterstoRead and

ul StartRegister*/

for (i=0; i < us_NumberRegisterstoRead; i++){</pre>

reg mca.us[ul StartRegister+i] = rbuf.us[READ DATA WORD OFFSET+i];

}

```

# **Revision History**

Tracking of the revision history begins with Rev A1

#### Revision A2

- changed the title to add supported Firmware revisions;

- updated the Baud Rate settings on Page 7;